This data sheet should be read in conjunction with NORBIT 2 Series

#### DESCRIPTION

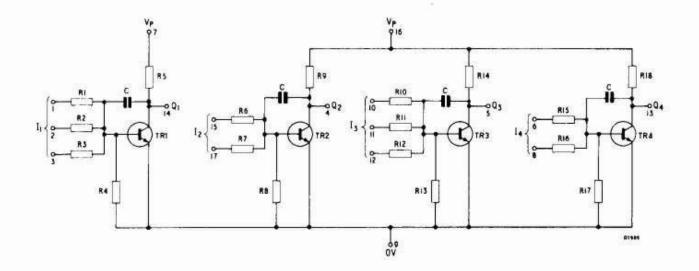

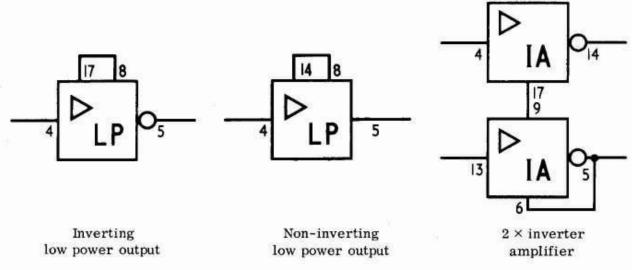

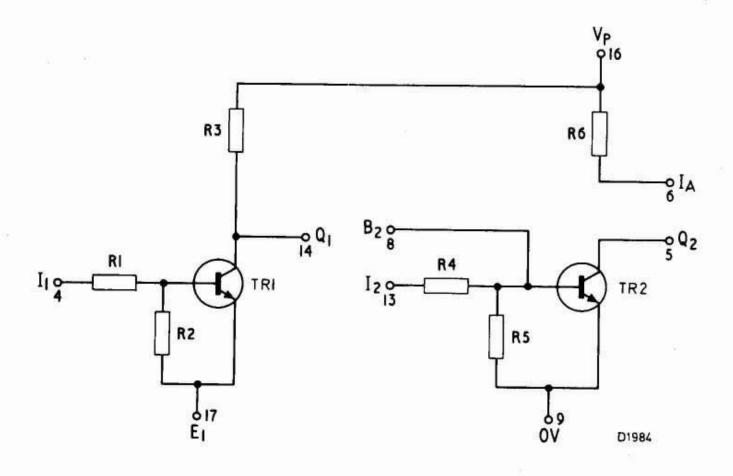

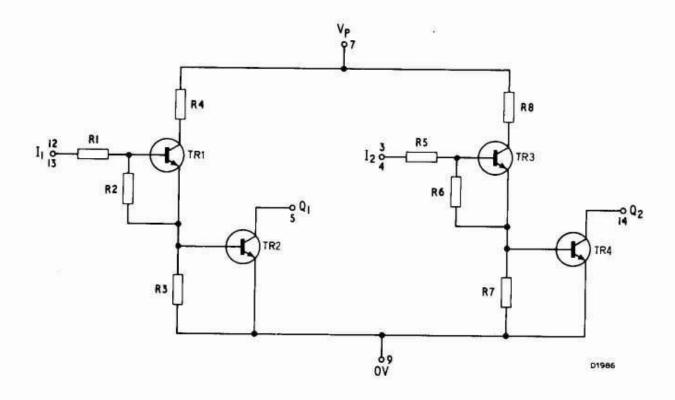

The unit comprises two inverter amplifiers which may be interconnected to form either a single inverting low power output unit or a single non-inverting low power output unit.

#### COLOUR

Blue

# ELECTRICAL DATA

#### Power supply

Supply voltage,  $V_p$  +24 ± 25%  $V_{d.c.}$  Supply current to pin 16 max. 31 mA  $\leftarrow$

# Input

Logic '0'  $0 \text{ to } 0.3 \qquad \text{V}$  Logic '1'  $+(0.24\text{V}_{\text{p}} + 7.2) \text{ to } \text{V}_{\text{p}} \qquad \text{V}$  Loading per input (all functions)  $2 \qquad \text{d.u.}$

#### Output

Loading per inverter amplifier output 20 d.u.

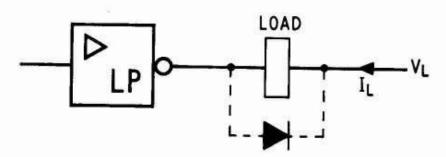

Loading, when used as load driver (see figs. 1 and 2)

Load voltage max. 30 V

Load current max. 100 mA

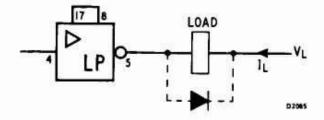

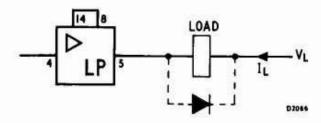

Logic '1' at the input, energises the load Fig. 1 Logic '0' at the input, energises the load Fig. 2

#### NOTES

- A diode must be used with inductive loads; suitable diodes are: BAX12, BAX13 or BAX16.

- 2. When driving filament lamps, series and bleed resistors must be used.

#### TERMINAL CONNECTIONS

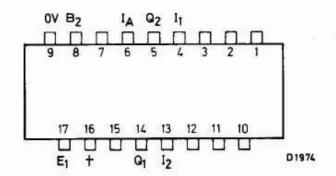

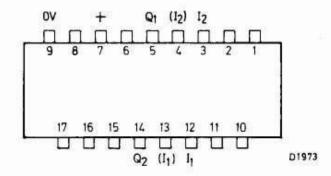

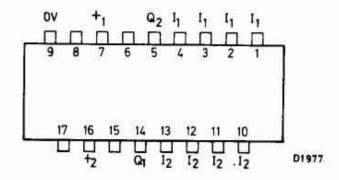

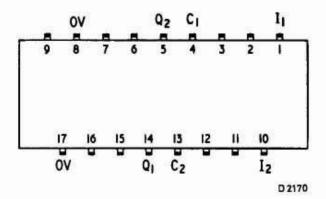

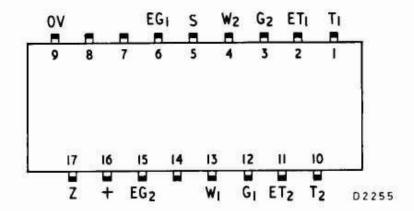

view from underside of module

| Terminal Connected to |                                            | Terminal<br>number | Connected to              |  |

|-----------------------|--------------------------------------------|--------------------|---------------------------|--|

| 1                     | Not connected                              | 10                 | Not connected             |  |

| 2                     | Not connected                              | 11                 | Not connected             |  |

| 3                     | Not connected                              | 12                 | Not connected             |  |

| 4                     | Input to IA 1 (I <sub>1</sub> )            | 13                 | Input to IA 2 (I2)        |  |

| 5                     | Output from IA 2 (Q2)                      | 14                 | Output from IA 1 (Q       |  |

| 6                     | 6 Collector resistor TR2 (I <sub>A</sub> ) |                    | Not connected             |  |

| 7                     | 7 Not connected*                           |                    | Positive supply $V_p$ (+) |  |

| 8                     | 8 Base of TR2 (B <sub>2</sub> )            |                    | Emitter of TR1 (E1)       |  |

| 9                     | Common supply (0V)                         |                    |                           |  |

\*CAUTION When mounted on PCB60, pin 7 is connected to the positive supply (Vp). Hence, ensure that pins 7 and 8 are not interconnected otherwise damage to TR2 will result.

# This data sheet should be read in conjunction with NORBIT 2 Series

#### DESCRIPTION

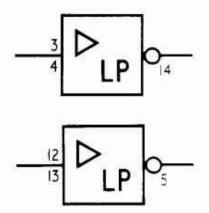

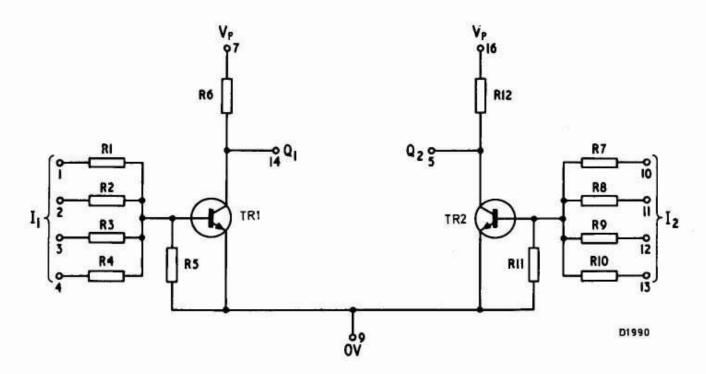

Two electrically independent inverting output driven circuits. The circuits are suitable for driving relays and small lamps.

COLOUR

Blue

mA

# ELECTRICAL DATA

# Power supply

Load current

Supply voltage, Vp +24 ± 25% Vd.c. Supply current to pin 7 max. 20 mA Input Logic '0' 0 to 0.3 V Logic '1' +(0.24V<sub>P</sub> +7.2) to V<sub>P</sub> Loading per input d.u. Output (see fig. 1) Load voltage max. 30 V

max.

100

Logic '1' at the input will energise the load Fig. 1

#### NOTES

- 1. The load must be connected as shown to output pins 5 or 14 as required.

- A diode must be used with inductive loads; suitable diodes are: BAX12, BAX13 or BAX16.

- 3. When driving filament lamps, series and bleed resistors must be used.

# TERMINAL CONNECTIONS

view from underside of module

| Terminal Connected to |                                                | Terminal<br>number | Connected to                                     |  |

|-----------------------|------------------------------------------------|--------------------|--------------------------------------------------|--|

| 1                     | Not connected                                  | 10                 | Not connected                                    |  |

| 2                     | Not connected                                  | 11                 | Not connected                                    |  |

| 3                     | Input to LPA 2 (12)                            | 12                 | Input to LPA 1 (I1)                              |  |

| 4                     | Internally connected to pin 3 $(\mathbf{I}_2)$ | 13                 | Internally connected to pin 12 (I <sub>1</sub> ) |  |

| 5                     | Output from LPA 1 (Q <sub>1</sub> )            | 14                 | Output from LPA 2 (Q2                            |  |

| 6                     | Not connected                                  | 15                 | Not connected                                    |  |

| 7                     | Positive supply V <sub>P</sub> (+)             | 16                 | Not connected                                    |  |

| 8                     | Not connected                                  | 17                 | Not connected                                    |  |

| 9                     | Common supply (0V)                             |                    |                                                  |  |

# This data sheet should be read in conjunction with NORBIT 2 Series

#### DESCRIPTION

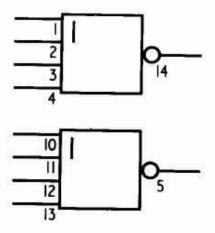

Two electrically independent 4-input NOR circuits. If any input of a NOR is at the '1' level, then the output of that 'NOR' will be at the '0' level.

#### COLOUR

Black

#### ELECTRICAL DATA

# Power supply

Supply voltage,  $V_{\mathbf{p}}$  Supply current to pin 16 or 7

+24 ± 25% V<sub>d.c.</sub>

max. 4.8

mA ←

#### Input

Logic '0'

0 to +0.3

V

Logic '1'

$+(0.24V_{\rm P}+7.2)$  to  $V_{\rm P}$

P (1.2) to (P

Loading per input

d.u.

#### Output

Loading per output

d.u.

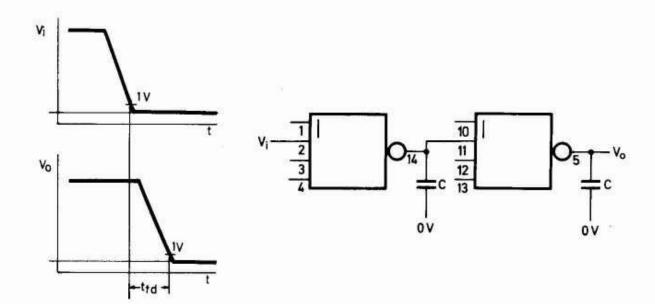

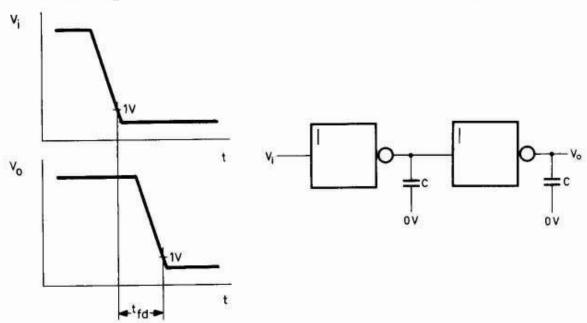

Propagation delay (tfd)

Over two stages

max.

6

μs

The delay time is defined as the time difference between the 1V points of the negative-going input and output voltages of two cascaded NOR's, each being loaded with 200pF.

# TERMINAL CONNECTIONS

view from underside of module

| Terminal<br>number | Connected to                                               |    | Connected to                            |  | Connected to |  |

|--------------------|------------------------------------------------------------|----|-----------------------------------------|--|--------------|--|

| 1                  | Input 1 to NOR 1 (11)                                      | 10 | Input 1 to NOR 2 (I2)                   |  |              |  |

| 2                  | Input 2 to NOR 1 (I1)                                      | 11 | Input 2 to NOR 2 (I2)                   |  |              |  |

| 3                  | Input 3 to NOR 1 (I <sub>1</sub> )                         | 12 | Input 3 to NOR 2 (I2)                   |  |              |  |

| 4                  | Input 4 to NOR 1 (1 <sub>1</sub> )                         | 13 | Input 4 to NOR 2 (I <sub>2</sub> )      |  |              |  |

| 5                  | Output from NOR 2 (Q2)                                     | 14 | Output from NOR 1 (Q1                   |  |              |  |

| 6                  | Not connected                                              | 15 | Not connected                           |  |              |  |

| 7                  | Positive supply, V <sub>P</sub> to NOR 1 (+ <sub>1</sub> ) | 16 | Positive supply, $V_p$ to NOR 2 $(+_2)$ |  |              |  |

| 8                  | Not connected                                              | 17 | Not connected                           |  |              |  |

| 9                  | Common supply (0V)                                         |    |                                         |  |              |  |

# NORBIT 2 TWIN INPUT SWITCH FILTER

# This data sheet should be read in conjunction with NORBIT 2 Series

#### DESCRIPTION

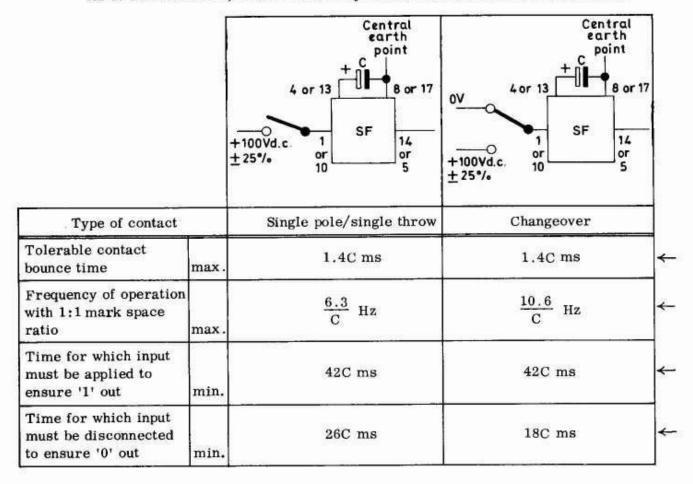

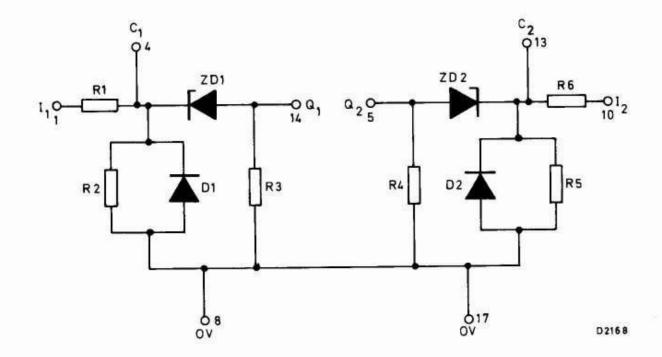

Two electrically independent filter circuits which may be used to suppress interference and eliminate the effects of contact bounce occurring on external switches, using an external capacitor. A high voltage is used to break down the contact film resistance of external switches.

COLOUR

Green

#### ELECTRICAL DATA

### Power supply

The logic supply is not connected to the unit; the 0V terminals (pins 8 or 17) should be connected to the central earth point.

#### Input

| Voltage for '1' out                 |             |      | $+100 \pm 25\%$ | Vd.c.             |

|-------------------------------------|-------------|------|-----------------|-------------------|

| Negative input voltage (under fault | conditions) | max. | -100            | V <sub>d.c.</sub> |

| Current per input                   | steady,     | max. | 3.5             | mA                |

|                                     | surge,      | max. | 4.8             | mA                |

# Output

Loading per output 2 d.u.

The output will be '1' when the input has been applied for longer than the time shown under "Operation" below. Similarly the output will be '0' within the appropriate time also given.

#### Operation

The external capacitor (C) should be connected between the appropriate terminals  $C_1$  and/or  $C_2$  and the common 0V terminal. The use of a 64V electrolytic capacitor is recommended, and its value may be obtained from the formulae below.

where C is the value of the external capacitor in  $\mu F$

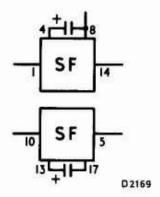

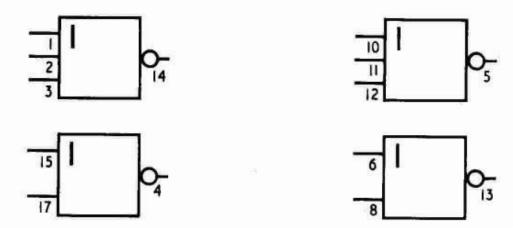

#### DRAWING SYMBOL

#### TERMINAL CONNECTIONS

view from underside of module

| Terminal<br>number | Connected to                    | Terminal<br>number | Connected to                    |

|--------------------|---------------------------------|--------------------|---------------------------------|

| 1                  | Input to SF1 (I <sub>1</sub> )  | 10                 | Input to SF2 (I <sub>2</sub> )  |

| 2                  | Not connected                   | 11                 | Not connected                   |

| 3                  | Not connected                   | 12                 | Not connected                   |

| 4                  | External capacitor for SF1 (C1) | 13                 | External capacitor for SF2 (C2) |

| 5                  | Output from SF2 (Q2)            | 14                 | Output from SF1 (Q1)            |

| 6                  | Not connected                   | 15                 | Not connected                   |

| 7                  | Not connected                   | 16                 | Not connected                   |

| 8                  | Common supply (0V)              | 17                 | Common supply (0V)              |

| 9                  | Not connected                   | 10                 | (internally connected to pin 8) |

# This data sheet should be read in conjunction with NORBIT 2 Series

#### DESCRIPTION

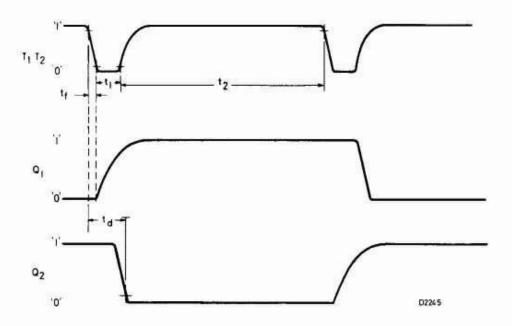

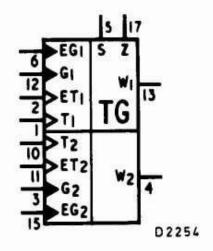

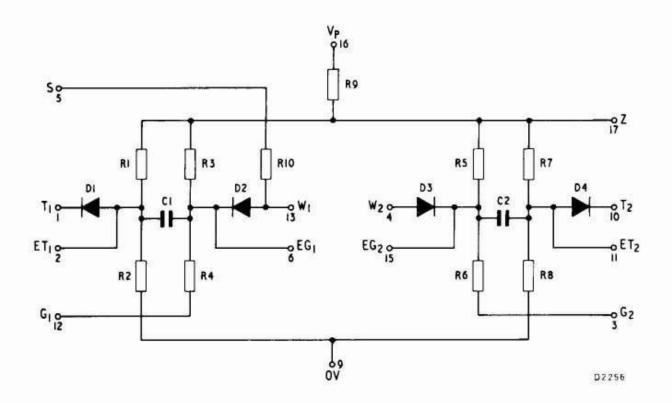

Two gating circuits to perform extra independent trigger functions for use with the flip-flop FF90. The mode of operation is the same as for the trigger functions of the FF90. Switching is performed by applying signals to the trigger terminals  $T_1$  and  $T_2$  and these signals are controlled by the gates  $G_1$  and  $G_2$  respectively. The trigger terminals may be expanded by the addition of diodes to the terminals  $ET_1$  and  $ET_2$  to provide an 'OR' or inhibit facility. The extra resistor (R10), connected to terminal  $W_1$ , provides the 'set' facility for the FF90.

The terminals EG1 and EG2 are not normally used.

COLOUR

Red

#### ELECTRICAL DATA

#### Power supply

| Supply voltage, V <sub>P</sub> |      | $+24 \pm 25\%$ | Vd.c. |

|--------------------------------|------|----------------|-------|

| Supply current to pin 16       | max. | 21             | mA ←  |

#### Input

| Logic '0' | 0 to 0.3                       | v |

|-----------|--------------------------------|---|

| Logic '1' | $+(0.24V_{D} +7.2)$ to $V_{D}$ | v |

#### Loading

The 2TG90 introduces pulse logic to the NORBIT 2 range and, because of the circuits used, the ability of the driving block to accept current at the '0' level must be considered. This ability to obey the current and timing requirements is expressed simply in terms of 'z.u.'.Normal drive units, i.e., 'd.u.', must still be considered. The input requirements at the various terminals of the 2TG90 are given in table 1.

Table 1

| Function                                                  | Input                                                             | d.u.<br>'1' level | z.u.<br>'0' level | Notes                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------|-------------------------------------------------------------------|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set<br>(put Q <sub>2</sub> of<br>associated<br>FF90 to 1) | S                                                                 | 1                 | 0                 | The 'set' input may be expanded by using up to 3 suitable diodes on each input. The cathode of each diode is connected to the input. If the 'set' facility is used, the input must be held at '0' (and not left open circuit) except during the input period.                          |

| Gate                                                      | G <sub>1</sub> , G <sub>2</sub>                                   | 2                 | 1                 | '1' or open-circuit closes gate. '0' opens gate.                                                                                                                                                                                                                                       |

| Gate                                                      | G <sub>1</sub> , G <sub>2</sub><br>via diode<br>(Notes 1 and 2)   | 0                 | 1                 | '1' or open-circuit closes gate. '0' opens gate. The anode of the diode must be connected to the input                                                                                                                                                                                 |

| Trigger                                                   | т <sub>1</sub> , т <sub>2</sub>                                   | 0                 | 2                 | Only a negative-going $1/0$ edge occurring within $3\mu s$ provides the required signal. If $T_1$ and $T_2$ are interconnected, $4z.u.$ are required.                                                                                                                                  |

| Trigger                                                   | ET <sub>1</sub> , ET <sub>2</sub><br>via diode<br>(Notes 1 and 2) | 0                 | 2                 | Only a negative-going 1/0 edge occurring within 3µs provides the required signal. If ET <sub>1</sub> and ET <sub>2</sub> are interconnected, 4z.u. are required. A maximum of two diodes may be connected to each ET terminal. The anode of each diode must be connected to the input. |

# NOTES

- 1. Suitable diodes are: BAX13 or BAX16.

- 2. When used, the external diodes should be mounted as close as possible to the twin trigger gate.

# NORBIT 2 TWIN-TRIGGER GATE

The loadings in d.u. and z.u. for the units in the NORBIT 2 range are given in table 2 below. The d.u. capability remains exactly as specified in the corresponding data sheets.

Table 2

| Unit                               | d.u.<br>'1' level | z.u.<br>'0' level | Notes                                                                                                                                                                                               |

|------------------------------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOR of<br>2NOR60                   | 6                 | 12                | 2 inputs must be connected in parallel. Signal must be derived from a chain of units that includes either a PS90, an FF90 or a TU60.                                                                |

| 2IA60<br>as low<br>power<br>output | . 20              | 50                | Signal must be derived from a chain of units that includes either a PS90, an FF90 or a TU60. Both the inverting and non-inverting connections can be used, but pins 5 and 6 must be interconnected. |

| NOR of<br>4NOR60                   | 6                 | 0                 | No z.u. available. Therefore, these                                                                                                                                                                 |

| LPA60                              | -                 | 0                 | units must not be used to drive a                                                                                                                                                                   |

| PA60 and<br>HPA60                  | -                 | o                 | 2TG90 directly.                                                                                                                                                                                     |

| TU60                               | 5                 | 0                 |                                                                                                                                                                                                     |

| SF60                               | 2                 | 0                 |                                                                                                                                                                                                     |

| PS90                               | 6                 | 40                |                                                                                                                                                                                                     |

| FF90                               | 5                 | 7                 |                                                                                                                                                                                                     |

# Output

The outputs  $W_1$  and  $W_2$  are suitable only for use with one FF90;  $W_1$  and  $W_2$  should be connected to  $B_1$  and  $B_2$  respectively.

Inter-wiring capacitance

max.

50

pF

To ensure this the 2TG90 should be mounted as close as possible to the FF90.

#### Operational requirements

The signal at the gate must be present for at least the duration of its recovery time before the triggering edge is applied to  $T_1$  or  $T_2$ . It is permitted to change the gate signal simultaneously with the triggering edge.

| Fall time, t <sub>f</sub> | max. | 3 | μs |

|---------------------------|------|---|----|

| Pulse duration, t,        | min. | 5 | μs |

Maximum values in kHz for pulse repetition frequency at T terminals,  $\frac{1}{t_1 + t_2}$  are given in table 3.

Table 3

| Connection                                                                                                          | t <sub>2</sub> = t <sub>1</sub> | t <sub>2</sub> = 10t <sub>1</sub> |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------|

| Flip-flop with input applied to $T_1$ and $T_2$ connected together                                                  | 5.0                             | 7.0                               |

| Flip-flop with input to $T_1$ or $T_2$ , having $ET_1$ and $ET_2$ interconnected and with gate diodes as in table 1 | 5.0                             | 12.5                              |

Set pulse duration min. 50  $\mu s$

# NORBIT 2 TWIN-TRIGGER GATE

|    |        |     |     | 114  |

|----|--------|-----|-----|------|

| 77 |        | -4- |     | tics |

|    | ı o ro | CTA | me  | LICH |

|    |        |     | 110 |      |

| Trigger recovery time, to | typ. | 73  | μв |

|---------------------------|------|-----|----|

| 2                         | max. | 99  | μs |

| Gate recovery time        |      |     |    |

| gate directly connected   | typ. | 105 | μs |

|                           | max. | 137 | μв |

| with gate diodes          | typ. | 64  | μs |

|                           | max. | 77  | μв |

| Switching delay, t        | typ. | 3   | μв |

| 2g, 'd                    | max. | 8   | μв |

# DRAWING SYMBOL

view from underside of module

| Terminal<br>number | Connected to                               | Terminal<br>number | Connected to                               |

|--------------------|--------------------------------------------|--------------------|--------------------------------------------|

| 1                  | Trigger input (T1)                         | 10                 | Trigger input (T2)                         |

| 2                  | Extension trigger input (ET <sub>1</sub> ) | 11                 | Extension trigger input (ET2)              |

| 3                  | Gate input (G <sub>2</sub> )               | 12                 | Gate input (G1)                            |

| 4                  | Output to flip-flop pin 4 (W2)             | 13                 | Output to flip-flop pin 13 (W1)            |

| 5                  | Set terminal (S)                           | 14                 | Not connected                              |

| 6                  | Extension gate input (EG1)                 | 15                 | Extension gate input (EG <sub>2</sub> )    |

| 7                  | Not connected                              | 16                 | Positive supply, V <sub>p</sub> (+)        |

| 8                  | Not connected                              | 17                 | Voltage reference terminal                 |

| 9                  | Common supply (0V)                         |                    | (connected to pin 17 on flip-<br>flop) (Z) |

# This data sheet should be read in conjunction with NORBIT 2 Series

#### DESCRIPTION

Two electrically independent 2-input NOR circuits and two 3-input NOR circuits. If any input of a NOR is at the '1' level, then the output of that 'NOR' will be at the '0' level.

COLOUR Black

#### ELECTRICAL DATA

#### Power supply

| Supply voltage, V <sub>P</sub> |      | $+24 \pm 25\%$ | $v_{d.c.}$          |

|--------------------------------|------|----------------|---------------------|

| Supply current to pin 7        | max. | 4.8            | $mA \leftarrow$     |

| Supply current to pin 16       | max. | 14.4           | $mA \longleftarrow$ |

#### Input

| Logic '0'         | 0 to +0.3                     | V    |

|-------------------|-------------------------------|------|

| Logic '1'         | $+(0.24V_{p}+7.2)$ to $V_{p}$ | V    |

| Loading per input | 1                             | d.u. |

#### Output

Loading per output 6 d.u.

# Propagation delay (tfd)

Over two stages max. 26  $\mu s$

The delay time is defined as the time difference between the 1V points of the negative-going input and output voltages of two cascaded NOR's, each being loaded with  $200 \mathrm{pF}$ .

# DRAWING SYMBOL

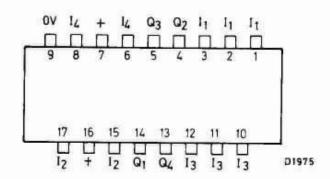

TERMINAL CONNECTIONS

view from underside of module

| Terminal<br>number | Connected to                                     | Terminal<br>number | Connected to                                             |

|--------------------|--------------------------------------------------|--------------------|----------------------------------------------------------|

| 1                  | Input to NOR 1 (I1)                              | 10                 | Input to NOR 3 (I3)                                      |

| 2                  | Input to NOR 1 (I <sub>1</sub> )                 | 11                 | Input to NOR 3 (I3)                                      |

| 3                  | Input to NOR 1 (I <sub>1</sub> )                 | 12                 | Input to NOR 3 (I3)                                      |

| 4                  | Output of NOR 2 (Q2)                             | 13                 | Output of NOR 4 (Q4)                                     |

| 5                  | Output of NOR 3 (Q3)                             | 14                 | Output of NOR 1 (Q <sub>1</sub> )                        |

| 6                  | Input to NOR 4 (I <sub>4</sub> )                 | 15                 | Input to NOR 2 (I2)                                      |

| 7                  | Positive supply, $V_{\overline{P}}$ to NOR 1 (+) | 16                 | Positive supply, V <sub>P</sub> to<br>NOR 2, 3 and 4 (+) |

| 8                  | Input to NOR 4 (I4)                              | 17                 | Input to NOR 2 (I2)                                      |

| 9                  | Common supply (0V)                               | 1                  | -                                                        |