## SERIES 54S/74S PROGRAMMABLE READ-ONLY MEMORIES

## step-by-step programming procedure for the 'S188, 'S287, 'S288, 'S387, 'S470 through 'S475

- 1. Apply steady-state supply voltage ( $V_{CC} = 5 \text{ V}$ ) and address the word to be programmed.

- 2. Verify that the bit location needs to be programmed. If not, proceed to the next bit.

- 3. If the bit requires programming, disable the outputs by applying a high-logic-level voltage to the chip-select input(s).

- 4. Only one bit location is programmed at a time. Connect each output not being programmed to 5 V through  $3.9 \mathrm{k}\Omega$  and apply the voltage specified in the table to the output to be programmed. Maximum current out of the programming output is 150 mA. This current flows from the programmer into the PROM output.

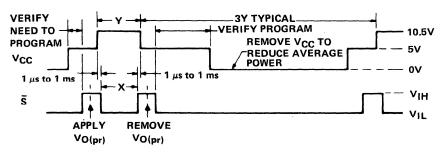

- 5. Step VCC to 10.5 V nominal. Maximum supply current required during programming is 750 mA.

- 6. Apply a low-logic-level voltage to the chip-select input(s). This should occur between 1  $\mu$ s and 1 ms after V<sub>CC</sub> has reached its 10.5-V level. See programming sequence of Figure 2.

- 7. After the X pulse time is reached, a high logic level is applied to the chip-select inputs to disable the outputs.

- 8. Within 1  $\mu$ s to 1 ms after the chip-select input(s) reach a high logic level, V<sub>CC</sub> should be stepped down to 5 V at which level verification can be accomplished.

- 9. The chip-select input(s) may be taken to a low logic level (to permit program verification) 1  $\mu$ s or more after V<sub>CC</sub> reaches its steady-state value of 5 V.

- 10. At a Y pulse duty cycle of 35% or less, repeat steps 1 through 8 for each output where it is desired to program a

NOTE: Only one programming attempt per bit is recommended.

LOAD CIRCUIT FOR EACH OUTPUT NOT BEING PROGRAMMED OR FOR PROGRAM VERIFICATION

FIGURE 1 - LOAD CIRCUIT

FIGURE 2 - VOLTAGE WAVEFORMS FOR PROGRAMMING