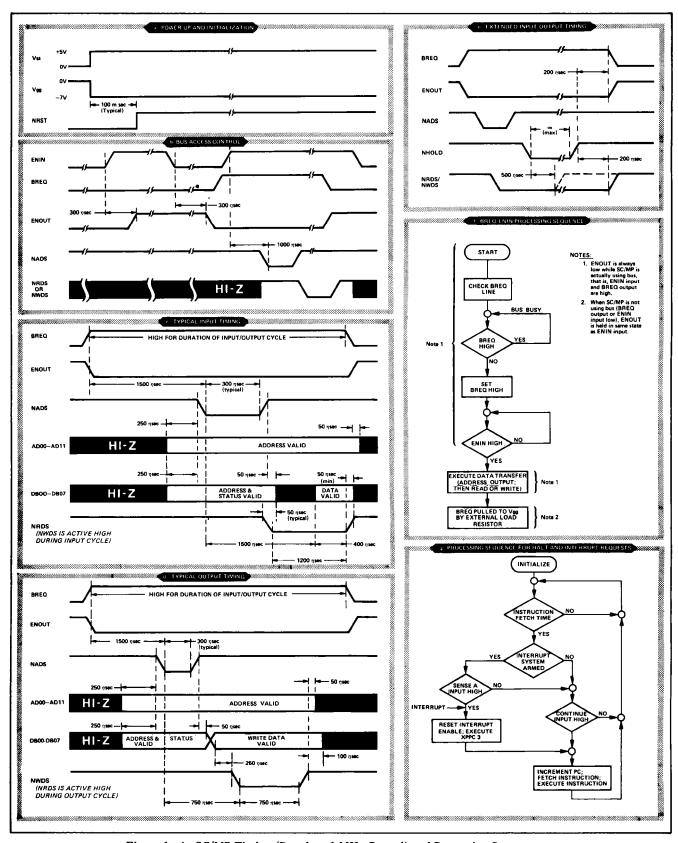

Figure 1-4. SC/MP Timing (Based on 1-MHz Crystal) and Processing Sequences

Table 1-1. Description of SC/MP Pinouts

| PIN                                      | Basic<br>Function                                               | Design Considerations                                                                                                                                                                                                                                                                 | PIN                      | Basic<br>Function             | Design Considerations                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1<br>37<br>X2                           | Timing                                                          | Connect capacitor between these pins for applications where timing is not critical; use crystal where timing is                                                                                                                                                                       | NRST                     | Negative<br>Reset             | When this input is set low, in-process operations are aborted.                                                                                                                                                                                                                          |

| 38                                       |                                                                 | critical. (Refer to Appendix A for component characterization and the use of an external clock.)                                                                                                                                                                                      | NHOLD<br>6               | Wait                          | In conjunction with CONT, the NHOLD input can be used to implement single cycle/single-instruction control of SC/MP — refer to figure 1-4e for extended input/                                                                                                                          |

| V <sub>SS</sub><br>20<br>V <sub>CC</sub> | Power                                                           | $V_{SS} = +5V (\pm 5\%)$ $V_{GG} = -7V (\pm 5\%)$                                                                                                                                                                                                                                     |                          |                               | output timing.                                                                                                                                                                                                                                                                          |

| V <sub>GG</sub>                          |                                                                 | VGG = ~/V (±5%)                                                                                                                                                                                                                                                                       |                          |                               |                                                                                                                                                                                                                                                                                         |

| Sense A<br>17<br>Sense B                 | External<br>sensing and<br>software-<br>controlled<br>interrupt | These TTL-level inputs are connected directly to bit positions 4 and 5 of the status register. Both bits can be copied from the status register to the accumulator but neither bit can be written into from the accumulator, that is, they are "read only" inputs. With the interrupt | SIN<br>23<br>SOUT<br>24  | Serial Input/<br>Output       | When the SIO instruction is executed, the MSB of the input data is shifted into the MSB of the extension register, and the LSB is shifted from the E-Register to an output latch, that is, the contents of the register can be changed without affecting the state of the output latch. |

|                                          |                                                                 | armed (bit 3 of status register set high), the Sense A pin becomes the interrupt input — see figure 1-4g for processing sequence of interrupt request and Appendix C for implementation detail of the interrupt system.                                                               | NADS                     | Negative<br>Address<br>Strobe | When low, indicates valid address and status outputs are present on the system buses. The NADS leading edge of the strobe can be used to externally latch input/output status and the four MSB of the 16-bit address; refer to fig-                                                     |

| Flag 0<br>19<br>Flag 1                   | External control of peripherals                                 | Each flag output is TTL-compatible and can drive a 1.6-milliampere load. The flags are software-controlled and can be                                                                                                                                                                 |                          |                               | ures 1-4c, 1-4d, and 1-4e for I/O timing of NADS.                                                                                                                                                                                                                                       |

| 21<br>Flag 2<br>22                       |                                                                 | set or pulsed in a single or multiple sequence.                                                                                                                                                                                                                                       | NRDS<br>2                | Negative<br>Read Strobe       | A Tri-State output that, when low, indicates SC/MP is ready to accept data from the 8-bit input/output bus; as shown in figure 1-4c, data are input on                                                                                                                                  |

| BREQ<br>ENIN                             | Bus-Access,<br>DMA, and<br>Multiprocessor                       | In simple stand-alone applications,<br>BREQ can be connected to V <sub>GG</sub> through<br>a 6.8 kilohm resistor, ENOUT can be ig-                                                                                                                                                    |                          |                               | the trailing edge of this strobe.                                                                                                                                                                                                                                                       |

| ENOUT                                    | Control                                                         | nored, and ENIN can be connected to V <sub>SS</sub> so that the SC/MP microprocessor has access to system buses whenever the BREQ pin is high. In systems that require bus-sharing, the common bus-request                                                                            | NWDS                     | Negative<br>Write Strobe      | A Tri-State output that, when low, indicates output data from SC/MP is valid on 8-bit input/output bus; refer to figure 1-4d for output timing.                                                                                                                                         |

|                                          |                                                                 | line is continually tested by each micro-<br>processor; when the request line is low,<br>system buses can be accessed, and if<br>BREQ and ENIN are set high, bus access<br>is granted.                                                                                                | DB 00-07                 | Input/Output<br>data          | At NADS time, I/O status and 4-MSB of 16-bit address are output from SC/MP; at NRDS time, data are input to SC/MP and, at NWDS time, data are output from SC/MP. Each pin is bidirectional                                                                                              |

| CONT<br>8                                | Start/Stop                                                      | Permits suspension of operations with-<br>out loss of internal status. Can be used<br>with 'HALT' flag to implement a pro-<br>grammed halt; also, can be used with<br>NHOLD (Wait) signal to implement<br>single-cycle/single-instruction control<br>of microprocessor.               | AD 00-<br>11<br>25<br>36 | Latched<br>Address            | and Tri-State.  At NADS time, the 12-bit latched address is valid and, as shown in figures 1-4c and 1-4d, a read or write function then is implemented.                                                                                                                                 |

<sup>\*</sup>Refer to SC/MP data sheet for minimum/maximum values.